### **TELEFUNKEN Semiconductors**

## MARC4 – 4-bit Microcontroller

The M43C201 is a member of the TEMIC family of 4-bit single chip microcontroller. It contains ROM, RAM, parallel I/O ports and on-chip clock generation.

### **Features**

#### • Stack oriented HARVARD architecture

- $-4K \times 8$ -bit ROM

- $-256 \times 4$ -bit RAM

- 2 μs instruction cycle

@ 4 MHz OSC-frequency

#### Programming

- User friendly in high level language qFORTH

## • Development system

- PC-based

- Highly optimising compiler

### Low power

- STOP mode @ 1 μA

- SLEEP mode typically 500 μA

- RUN mode typically 3 mA

### • High operating range

- Supply voltage range 2.4 to 6.2 V

- Temperature range -40 to 85°C

### • Interrupt structure

- − 1 prescaler/timer interrupt

- Software interrupts

- Autosleep

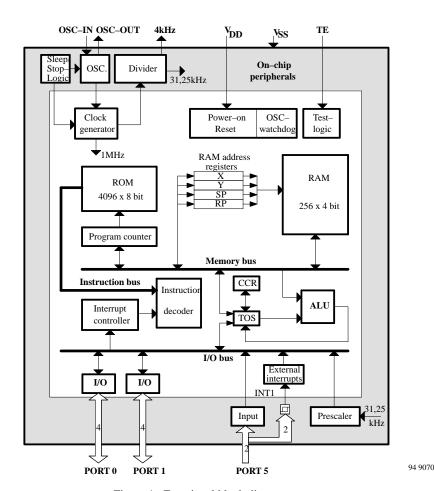

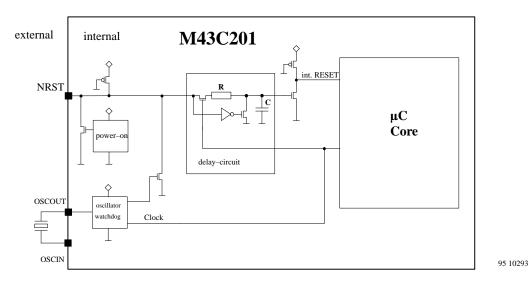

Figure 1. Functional block diagram

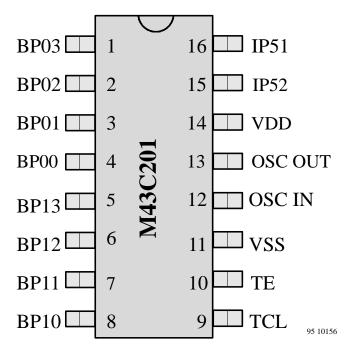

Figure 2. Pin assignment SO16 (top view)

Table 1. Pin description

| Name        | Function                                                                                          |

|-------------|---------------------------------------------------------------------------------------------------|

| $V_{DD}$    | Power supply voltage 2.4 to 6.2 V                                                                 |

| $V_{SS}$    | Circuit ground                                                                                    |

| BP00 - BP03 | 4 bidirectional I/O lines of port 0 *                                                             |

| BP10 – BP13 | 4 bidirectional I/O lines of port 1 *                                                             |

| IP50 - IP51 | 2 input lines of port 5                                                                           |

| OSCIN       | Oscillator input (32-kHz crystal)                                                                 |

| OSCOUT      | Oscillator output (32-kHz crystal)                                                                |

| TCL         | External system clock I/O. This pin can be used as input to provide the C with an external clock. |

| TE          | Testmode input. This input is used to control the test modes and the function of the TCL pin.     |

\*) The I/O ports have CMOS output buffers. As input they are available with pull-up or pull-down resistors. Please see the order information.

**Note:** For emulation use the M43C200 type in a SO24 case.

## M43C201

# TEMIC

**TELEFUNKEN Semiconductors**

## **Contents**

| 1 | Gene  | ral Descri                                             | ption                                               |  |  |  |  |  |

|---|-------|--------------------------------------------------------|-----------------------------------------------------|--|--|--|--|--|

|   | 1.1   | Interrup                                               | ot Structure                                        |  |  |  |  |  |

|   | 1.2   | Prescale                                               | er                                                  |  |  |  |  |  |

| 2 | Pin-, | Signal-, M                                             | Iemory-, Core Registers- and Self-Check Description |  |  |  |  |  |

|   | 2.1   | Pin Des                                                | scription                                           |  |  |  |  |  |

|   |       | 2.1.1                                                  | V <sub>DD</sub> , V <sub>SS</sub>                   |  |  |  |  |  |

|   |       | 2.1.2                                                  | TCL                                                 |  |  |  |  |  |

|   |       | 2.1.3                                                  | TE                                                  |  |  |  |  |  |

|   |       | 2.1.4                                                  | OSCIN, OSCOUT                                       |  |  |  |  |  |

|   |       | 2.1.5                                                  | Bidirectional Ports                                 |  |  |  |  |  |

|   |       | 2.1.6                                                  | Input Port 5                                        |  |  |  |  |  |

|   | 2.2   | Memor                                                  | y                                                   |  |  |  |  |  |

|   | 2.3   |                                                        | egisters                                            |  |  |  |  |  |

|   |       | 2.3.1                                                  | Accumulator (TOS)                                   |  |  |  |  |  |

|   |       | 2.3.2                                                  | Expression Stack Pointer (SP)                       |  |  |  |  |  |

|   |       | 2.3.3                                                  | RAM Address Register (X and Y)                      |  |  |  |  |  |

|   |       | 2.3.4                                                  | Return Stack Pointer (RP)                           |  |  |  |  |  |

|   |       | 2.3.5                                                  | Program Counter (PC)                                |  |  |  |  |  |

|   |       | 2.3.6                                                  | Condition Code Register (CCR)                       |  |  |  |  |  |

|   |       | 2.3.7                                                  | Self-Check                                          |  |  |  |  |  |

| • | D4    | . M. J T.                                              | waterway A. Deres less of J. or Deres W. J.         |  |  |  |  |  |

| 3 |       | Reset Modes, Interrupts, Prescaler and Low Power Modes |                                                     |  |  |  |  |  |

|   | 3.1   |                                                        | Modes                                               |  |  |  |  |  |

|   |       | 3.1.1                                                  | Power-on Reset                                      |  |  |  |  |  |

|   |       | 3.1.2                                                  | Oscillator – Watchdog Reset Function                |  |  |  |  |  |

|   |       | 3.1.3                                                  | Effects on Internal Circuitry                       |  |  |  |  |  |

|   |       | 3.1.4                                                  | Summary of all Reset Functions                      |  |  |  |  |  |

|   | 3.2   | -                                                      | ots                                                 |  |  |  |  |  |

|   |       | 3.2.1                                                  | Interrupt Handling                                  |  |  |  |  |  |

|   |       | 3.2.2                                                  | Interrupt Latency                                   |  |  |  |  |  |

|   |       | 3.2.3                                                  | Software Interrupts                                 |  |  |  |  |  |

|   |       | 3.2.4                                                  | Hardware Interrupts                                 |  |  |  |  |  |

|   | 3.3   |                                                        | er Interrupt                                        |  |  |  |  |  |

|   |       | 3.3.1                                                  | Prescaler during SLEEP Mode                         |  |  |  |  |  |

|   | 3.4   |                                                        | ower Modes                                          |  |  |  |  |  |

|   |       | 3.4.1                                                  | SLEEP Mode                                          |  |  |  |  |  |

|   |       | 3.4.2                                                  | STOP Mode                                           |  |  |  |  |  |

## M43C201

## **TELEFUNKEN Semiconductors**

## **Contents (continued)**

| 4 | Elect | rical Char  | acteristics                                                   | 16 |

|---|-------|-------------|---------------------------------------------------------------|----|

|   | 4.1   | Absolut     | e Maximum Ratings                                             | 16 |

|   | 4.2   | DC Ope      | erating Characteristics                                       | 16 |

|   |       | 4.2.1       | Supply Currents                                               | 16 |

|   |       | 4.2.2       | Power-on Reset (POR)                                          | 16 |

|   |       | 4.2.3       | DC Electrical Characteristics, V <sub>DD</sub> = 2.4 V @ 25°C | 17 |

|   |       | 4.2.4       | DC Electrical Characteristics, V <sub>DD</sub> = 6.2 V @ 25°C | 17 |

|   |       | 4.2.5       | Oscillator                                                    | 18 |

|   | 4.3   | I/O Port    | t Characteristics                                             | 19 |

| 5 | Char  | acteristics | of the On-Chip Quartz / Ceramic Oscillator                    | 23 |

| 6 | Char  | acteristics | of the Schmitt-Trigger Inputs                                 | 24 |

| 7 | Orde  | ring Infor  | mation                                                        | 25 |

## 1 General Description

The M43C201 is a member of the TEMIC MARC4 family (single chip Modular ARChitecture 4-bit microcomputers). It contains ROM, RAM, I/O ports, 15 stage prescaler, 4 MHz oscillator and 2 external interrupts.

**Note:** About 0.5 Kbyte of the 4 K ROM are required for the self-test program.

The CPU is built around a stack based Harvard type architecture, where the program memory (in ROM) and the data memory (in RAM) are physically separated and addressed independently.

The M43C201 has a typical instruction cycle time of 2  $\mu$ s @ 4 MHz oscillator frequency.

The SLEEP instruction allows the CPU to be stopped by the program, thereby enabling reduction in current consumption. Once the CPU has entered SLEEP mode it can be revived into active state immediately, following the receipt of an interrupt. In SLEEP mode, the CPU is held in a defined state whereby all data are latched. In the SLEEP mode the 4-MHz oscillator and the prescaler/timer are still running. It gives the opportunity to wake up the CPU in a defined time which is given by the prescaler.

The highest power saving mode is the STOP mode. In this case the CPU, oscillator and prescaler are all stopped controlled by the internal NRUN signal. If an interrupt

appears the 4-MHz oscillator will be started, controlled by the SLEEP/STOP logic. When the oscillator has reached the exact frequency a reset is generated and the program will start the \$RESET routine.

## 1.1 Interrupt Structure

The MARC4 can handle up to 8 priority interrupts which can be generated from on-chip modules (prescaler), external sources (interrupt pad) or synchronously from the CPU itself (software interrupts).

An additional power-on reset interrupt is used for initialising the CPU. The purpose of the power-on reset is to start the oscillator and to put the CPU into a well defined condition after the operating voltage has been reached. The reset interrupt has the absolute highest priority having access to the CPU at all times. The processor will automatically enter SLEEP when the lowest priority task has been completed, so making maximum use of the power saving capabilities of the MARC4.

### 1.2 Prescaler

A programmable prescaler driven by 31.25 kHz offers 1 interrupt. Table 2 (page 14) illustrates the eligible interrupt frequencies. The prescaler powers up in the reset condition.

Rev. A1: 26.06.1995 5 (26)

## 2 Pin-, Signal-, Memory-, Core Registers- and Self-Check Description

## 2.1 Pin Description

## $2.1.1 \quad V_{DD}, V_{SS}$

$V_{DD}$  is the power for the  $\mu C$  core, RAM, ROM and the peripherals,  $V_{SS}$  is ground.

#### 2.1.2 TCL

The system clock for the microprocessor is derived from a fully integrated on-chip crystal oscillator circuit. This oscillator tracks the supply and temperature to ensure optimum operation of the microcontroller under all conditions.

The TCL pin is necessary as clock input for the test- and emulation mode.

#### 2.1.3 TE

These line is needed for test and emulation.

### 2.1.4 OSCIN, OSCOUT

An oscillator with a divider stage is integrated in the chip to generate the 1 MHz clock frequency (TCL). This oscillator is operated by simple connection of 4 MHz quartz or ceramic resonator.

This oscillator can be controlled via port 42 (NRUN-signal). This means that the oscillator can be stopped in SLEEP mode or remains active if operation of the prescaler is desired. However, this function can only be set by software.

INRUN - signal "high"

the  $\mu$ C goes in sleep mode after finishing the lowest (Port 42) interrupt (oscillator running).

INRUN - signal "low"

the  $\mu C$  goes in STOP mode after finishing the lowest interrupt (oscillator stop).

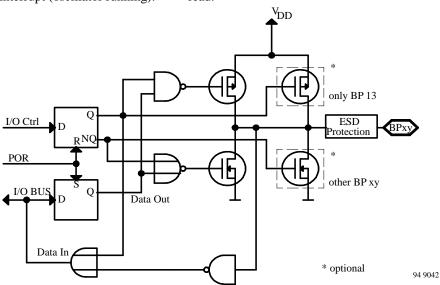

#### 2.1.5 Bidirectional Ports

Port 0 and 1 may be programmed as an input or an output under software control. The direction of a port is determined by an IN or OUT instruction and is held until another IN or OUT instruction for this port is executed.

The direction of this bidirectional ports is not switchable on a bit-wise basis. The output latches hold the state of last data value written to the port. At power-on or external reset all pins of port 0 and 1 are set to input mode and all output latches are set to a logic 1.

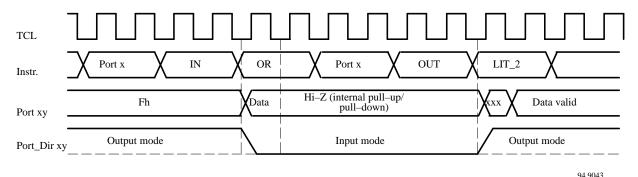

Whenever the port is switched from input to output the last value stored in the latches will appear on the outputs for one clock cycle (figure 4).

When switching bidirectional ports from output to input the stray capacitance of the connection wires may cause the data read to be the same as the last data written to this port. This behaviour can be used by connecting large enough capacitors to the pins of the bidirectional port to read back the previous data written to this port.

On the other hand, to avoid the negative effects of stray capacitance the following approaches should be used: Use two IN instructions, and DROP the first data nibble read.

Figure 3. Bidictional port schematics

**TELEFUNKEN Semiconductors**

xxx ) Last written data contained in output latches, Fh after power-on-reset

Figure 4. Read and write cycle timing

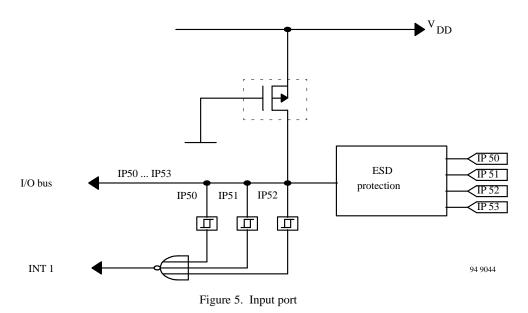

### **2.1.6** Input Port 5

The data on port 5 is sent to the top of the expression stack whenever an IN instruction (addressing port 5) is executed. The pins IP51 and IP52 of the port 5 may generate an additional interrupt (priority level 1), when any of the three input lines is driven low. This function is useful for implementing an interrupt driven keyboard. The interrupt lines are negative edge triggered and have Schmitt-trigger characteristics to improve the noise immunity. The interrupt function is enabled after power-on or external reset. This interrupt can be disabled by software.

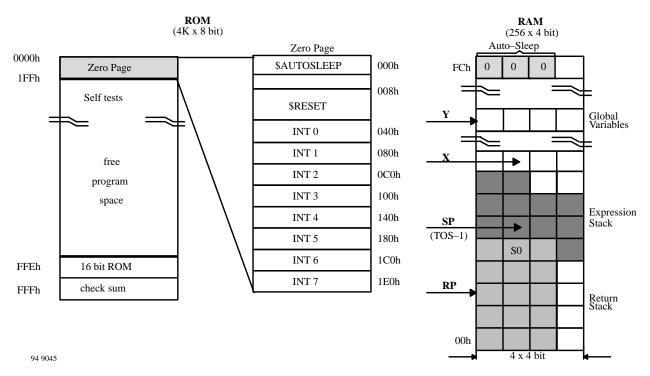

## 2.2 Memory

The MARC4 family of microcontroller is based on the Harvard architecture with physically separate program memory (ROM) and data memory (RAM).

The program memory (ROM) is mask programmed with the customer application program during the fabrication of the microcontroller. The ROM is addressed by a 12-bit wide program counter, thus limiting the program size to a maximum of 4096 bytes which cannot be extended by using external memory. The user ROM starts with a 512 byte segment ('Zero Page') which contains predefined start addresses for interrupt service routines and special subroutines accessible with single byte (SCALL) instructions. The corresponding memory map is shown in figure 6.

The self test routines should be included as part of the free program space. The 16-bit check sum (CRC) is located by the compiler in the last two bytes of ROM.

The on-chip  $256 \times 4$ -bit RAM is divided in the 12-bit wide return stack, the 4-bit wide expression stack (both with a user definable depth) and the data memory. The fixed return address (00h) which points to the \$AUTO-SLEEP routine is located at RAM address FCh.

Rev. A1: 26.06.1995 7 (26)

Figure 6. Memory map

## 2.3 Core Registers

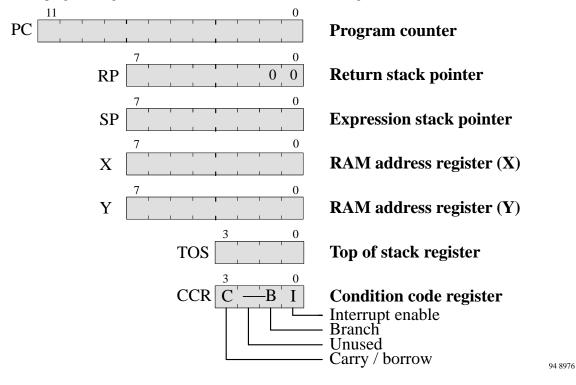

As shown in the programming model below, the MARC4 core has seven registers.

Figure 7. Programming model

### 2.3.1 Accumulator (TOS)

Because this microcontroller is a stack based machine with two on-chip stacks located in the internal RAM, all arithmetic , I/O and memory reference operations take their operands from, and return their results to the 4-bit wide expression stack. This stack is also used for passing parameters between subroutines, and as a scratchpad area for temporary storage of data. The top element of the expression stack is immediately accessible through the TOS register. The MARC4 can perform most of the operations dealing with the top of stack items (TOS and TOS-1) in a single byte, single cycle instruction.

## 2.3.2 Expression Stack Pointer (SP)

The 8-bit wide stack pointer SP contains the address of the next-to-top 4-bit item (TOS-1) on the expression stack, located in internal RAM. After power-on reset the stack pointer has to be initialised to the start address of the allocated expression stack area (S0).

### 2.3.3 RAM Address Register (X and Y)

The 8-bit wide register X and Y are used to address any 4-bit item in the RAM.

Using either the pre-increment address mode it is comfortable to compare, fill or move arrays in the RAM area.

### 2.3.4 Return Stack Pointer (RP)

The return stack pointer (RP) points to the top element of the return stack.

The 12-bit return stack is used for storing subroutine return addresses and keeping loop index counts. The return stack can also be used as a temporary storage area. The MARC4 instruction set supports the exchange of data between the top elements of the expression and return stack. The return stack automatically pre-increments and post-decrements in steps of 4. This means that every time a subroutine return address is stacked, 4-bit RAM locations are left unwritten. This locations are used by the qFORTH compiler to allocate 4-bit variables.

After power-on reset the return stack pointer has to be initialised to FCh.

#### 2.3.5 Program Counter (PC)

The program counter (PC) is a 12-bit register that contains the address of the next instruction to be executed by the microcontroller.

### 2.3.6 Condition Code Register (CCR)

The 4-bit wide condition code register (CCR) indicates the results of instruction just executed as well as the state of the microcontroller. These bits can be individually tested by a program and specified action will take place as a result of their state. Each bit is explained in the following paragraphs.

#### Carry/Borrow (C)

This flag indicates that a borrow or carry out of the arithmetic logic unit (ALU) occurred during the last arithmetic operation. This bit is also affected during shift and rotate operations and the execution of SET\_BCF, CLR BCF and CCR! instructions.

#### Zero (Z)

When the bit is set, it indicates that the result of the last arithmetic or logical manipulation was zero.

#### Branch (B)

A conditional branch takes place when the branch flag was set by one of the previous instructions (e.g., a comparison operation).

Instructions such as SET\_BCF, TOG\_BF and CLR\_BCF allow the direct manipulation of the branch flag under program control. The flag is affected by all ALU operations except CCR@, DI, SWI, RTI and OUT.

### Interrupt enable (I)

This flag is used to interrupt processing on global basis. Resetting the interrupt enable flag (using the DI instruction) disables all interrupts. The  $\mu C$  does not process further interrupt requests until the interrupt enable flag is set again by either executing an EI, RTI (return-from-interrupt) instruction or entering the SLEEP mode. After power-on or an external reset the interrupt enable flag is automatically reset. The RTI instruction at the end of the \$RESET routine will set the interrupt enable flag and thereby enable all interrupts.

#### 2.3.7 Self-Check

The self test capability of the MARC4 provides the possibility of checking the core, ROM, RAM, interrupt and prescaler easily. The \$RESET routine (after power-on reset) allows to choose the test routine or the application program.

**Note:** The necessary test routine were delivered by TEMIC.

Rev. A1: 26.06.1995 9 (26)

## 3 Reset Modes, Interrupts, Prescaler and Low Power Modes

### 3.1 Reset Modes

The M43C201 has two reset modes: a power-on and an oscillator watchdog reset function.

### 3.1.1 Power-on Reset

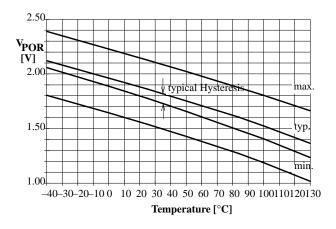

The power-on reset occurs when a positive transition is detected on the power supply input. The power-on reset is used strictly for power turn-on conditions and should not be used to detect any drops in the power supply voltage. A power-down reset occurs when a negative transition is detected on the power supply input for 5 ms or more. To improve noise immunity the power-on reset has Schmitt-trigger characteristics as shown in figure 8.

Figure 8. Temperature vs. V<sub>POR</sub>

## 3.1.2 Oscillator – Watchdog Reset Function

The oscillator-watchdog guarantee a well-defined clock condition by using a quartz or a ceramic resonator.

After starting, normally this sorts of oscillator generates undefined clock signals. In this case the amplitude is controlled by the oscillator-watchdog. When the right value of oscillator-amplitude is detected the RST pin will be hold LOW for 32 oscillator periods. After this time the uC starts the \$RESET-routine.

When extern clock is used (pin OSCOUT as clock input) the amplitude must be  $0.9 \times V_{DD}$  otherwise the oscillator watchdog will detect an error.

### 3.1.3 Effects on Internal Circuitry

All reset modes guarantee a well-defined start condition of the complete microcontroller. During RESET all interrupts are disabled, all pending and active interrupts are cleared, all on-chip peripherals are reset and a non-maskable interrupt request is generated. The RESET has the absolute highest priority, having access to the microcontroller at all times.

|         | Function                           | Located<br>in ROM<br>at | Max.<br>Length<br>[ROM<br>Bytes] | Interrupt<br>Opcode |

|---------|------------------------------------|-------------------------|----------------------------------|---------------------|

| \$RESET | Software & hardware initialization | 008h                    | 56                               | C1h                 |

The main tasks of the reset service routine (\$RESET) are:

- Stack pointer initialization,

- Variable and array initialization, and

- Initialisation and setup of the peripherals.

After execution of the reset service routine, the interrupts are enabled automatically by the RTI or previously executed EI instruction.

Figure 9. Reset functions

## 3.1.4 Summary of all Reset Functions

Figure 9 shows all reset functions: power-on and oscillator-watchdog. All these resets will generate an internal reset after passing the delay circuit. Normally the delay time is about 40 periods of the system frequency (TCL).

## 3.2 Interrupts

The M43C201 can handle interrupts of 8 priority levels (table 1). They are generated from on-chip modules (prescaler), external source (port 5) or synchronously from the core itself (software interrupts). Each interrupt source has a hard-wired interrupt priority and an associated interrupt service routine in the program ROM. The programmer can enable or disable all interrupts by setting or resetting the interrupt enable flag in the CCR using the EI or DI instruction.

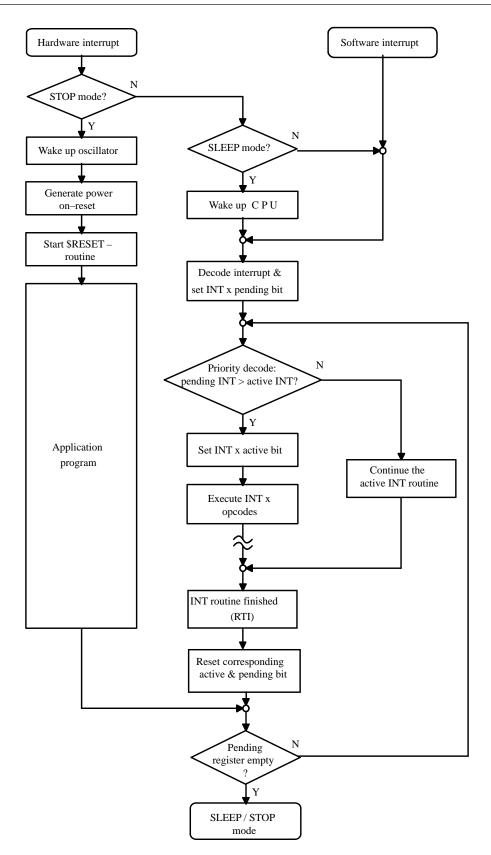

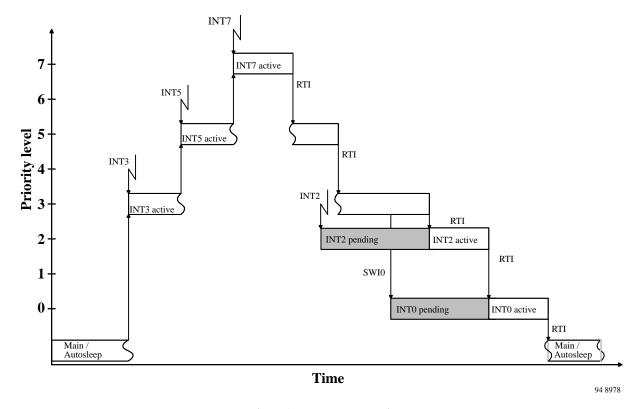

When the interrupt enable flag is reset (interrupts disabled), the execution of interrupts is inhibited but not the logging of the interrupt requests in the interrupt pending register. While interrupts are disabled (e.g., for a time critical section of code) and an interrupt is generated the interrupt will not be lost. Its execution will only be delayed until interrupts are enabled again. Interrupts are only lost when the pending register for a particular interrupt priority is still set at the time of a further interrupt transmission of the same level. The pending resister is reset either on power-on reset or on compilation of corresponding interrupt service routine by execution the RTI instruction (see figures 10 and 11).

The  $\mu C$  automatically enters the SLEEP mode when the lowest priority interrupt service routine has been completed. This guarantees a maximum use of the power saving capabilities of the  $\mu C$ . For further information please refer to low power modes.

Table 1. Interrupt priority and address allocation map

| Priority | Function                                                          | Located in ROM at | Max. Length [ROM bytes] | Interrupt<br>Opcode |

|----------|-------------------------------------------------------------------|-------------------|-------------------------|---------------------|

| INT7     | Software interrupt                                                | 1E0h              | > 24                    | FCh                 |

| INT6     | Software interrupt                                                | 1C0h              | 32                      | F8h                 |

| INT5     | Software interrupt                                                | 180h              | 64                      | F0h                 |

| INT4     | Prescaler interrupt                                               | 140h              | 64                      | E8h                 |

| INT2     | Software interrupt                                                | 0C0h              | 64                      | D8h                 |

| INT1     | External hardware interrupt negative edge triggered (port 51, 52) | 080h              | 64                      | D0h                 |

| INT0     | Software interrupt                                                | 040h              | 64                      | C8h                 |

94 9048

Figure 10. Interrupt flow chart

Figure 11. Interrupt processing

### 3.2.1 Interrupt Handling

The integrated interrupt controller samples all interrupt requests and latches these in the interrupt pending register. It also decodes the priority of the interrupt requests, and signals the  $\mu C$  when a higher priority interrupt requests is present. If the  $\mu C$  (with interrupts enabled) receives the interrupt controller's signal, an interrupt acknowledge cycle will be entered. During this cycle, the  $\mu C$  saves the current PC on the return stack and loads the PC with the start address of the corresponding interrupt service routine. When the  $\mu C$  is in the SLEEP mode, it will be activated by any hardware interrupt, by the means of wake-up the CPU and decoding the interrupt.

Using the MARC4 way of interrupt transmission, it is possible to transmit more than one interrupt at the same time. The transmitted interrupts are loaded into the interrupt pending register asynchronously. The priority decoder determines the interrupt with the highest priority and activates it as shown in figure 11. If the  $\mu$ C was in stop-mode any interrupt will start the oscillator. This will generate a reset and starts the \$RESET routine.

### 3.2.2 Interrupt Latency

The interrupt latency is the time from the falling edge of the interrupt to the interrupt service routine being activated. This time is between three or five instruction cycles depending on the state of the core. The highest frequency which can be reasonably handled on the duty cycle of the application.

### 3.2.3 Software Interrupts

Software interrupts are executable instructions which are supported by predefined macros named SWI 0 through SWI 7. The software triggered interrupts operates exactly like any hardware triggered interrupt.

#### 3.2.4 Hardware Interrupts

Any of the input port 51 and 52 may generate an interrupt level 1 (see figure 5). The INT1 is negative edge triggered and has Schmitt-trigger characteristics.

## 3.3 Prescaler Interrupt

The programmable prescaler is usually driven by an internal frequency of 31.25 kHz. The prescaler consists of a stage divider chain. This divider chain offers an interrupt source with the priority level 4. The prescaler module powers up in the reset condition which corresponds to control code Fh. The prescaler interrupt (INT4) has 15 programmable taps from 15.625 kHz down to 1 Hz. They are selectable by writing a value of E...0 into the control register at port address 15.

| Control Code Port Address 15 | Interrupt Frequency f <sub>C</sub> / n | $f_C = 31.25 \text{ kHz Time Interval}$ |

|------------------------------|----------------------------------------|-----------------------------------------|

| F                            |                                        | reset & hold compl. presc.              |

| E                            | $n = 2^1$                              | 64 μs                                   |

| D                            | $n=2^2$                                | 128 μs                                  |

| С                            | $n=2^3$                                | 256 μs                                  |

| В                            | $n=2^4$                                | 512 μs                                  |

| A                            | $n=2^5$                                | 1.024 ms                                |

| 9                            | $n = 2^6$                              | 2.048 ms                                |

| 8                            | $n=2^7$                                | 4.096 ms                                |

| 7                            | $n = 2^8$                              | 8.192 ms                                |

| 6                            | $n = 2^9$                              | 16.384 ms                               |

| 5                            | n = 2 <sup>10</sup>                    | 32.769 ms                               |

| 4                            | $n = 2^{11}$                           | 65.536 ms                               |

| 3                            | $n = 2^{12}$                           | 131.072 ms                              |

| 2                            | $n = 2^{13}$                           | 262.144 ms                              |

| 1                            | $n = 2^{14}$                           | 524.288 ms                              |

| 0                            | n = 2 <sup>15</sup>                    | 1.048 s                                 |

Table 2. Selectable interval times for the prescaler

## 3.3.1 Prescaler during SLEEP Mode

When the microcontroller enters the SLEEP mode, the core clocks are halted. While the 4 MHz oscillator and prescaler remain active, all  $\mu$ C actions are suspended. The microcontroller exists in the SLEEP mode when an interrupt is generated by the prescaler (in addition to a logic low on an external interrupt (INT3), port 50, 51, 52 input pin (INT1), or an external reset).

### 3.4 Low Power Modes

Two low power consumption modes of operation are available: SLEEP and STOP mode. These operating modes are initiated by executing the SLEEP instruction.

**Note:** The SLEEP instruction is not a normal instruction as its function is depended on the state of the interrupt pending register. SLEEP is therefore available for use within the \$AUTOSLEEP routine only.

### 3.4.1 SLEEP Mode

By executing the SLEEP instruction (in the \$AUTO-SLEEP routine) the microcontroller enters a low power consumption mode. In this SLEEP mode, the programmable prescaler remains active, while the internal  $\mu$ C-clock is turned off causing all core processing to be stopped. It can only be kept when none of the interrupt pending or active register bits are set.

During the SLEEP mode, the I bit in the condition code register (CCR) is set to enable all interrupts. All other

registers, memory, and parallel input/output lines remain the same. The 4 MHz oscillator is not switched off, but the prescaler may be disabled by the application program. This mode will continue until any interrupt or reset is sensed. At this time the event is decoded and the program counter is loaded with the corresponding starting address of the interrupt or reset service routine.

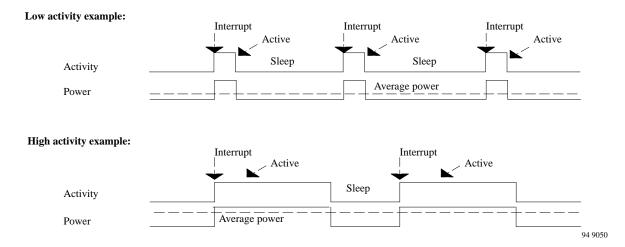

The MARC4 unique AUTOSLEEP feature allows the  $\mu C$  to enter the SLEEP mode automatically when the lowest priority interrupt service routine has been completed.

The SLEEP mode is a shutdown condition which is used to reduce the average system power consumption in applications where the  $\mu C$  is not fully utilised (figure 13). Using SLEEP and interrupts, the full computational speed of the core is always available. In this way, power is only consumed when needed, allowing the  $\mu C$  to run in high speed bursts from a weak supply (battery, capacitor, or even a solar cell).

### Calculating the average power consumption

The total power consumption is directly proportional to the active time of the  $\mu C$ . For a rough estimation of the expected average system current consumption, the following formula should be used:

$$I_{SYS} = I_{SLE} + (I_{DD} \times T_{active} / T_{total})$$

#### **3.4.2 STOP Mode**

The lowest power consumption mode of the microcontroller is entered with the STOP operation. The current consumption of the  $\mu C$  (without external loads) will be reduced to 1  $\mu A$ .

### **TELEFUNKEN Semiconductors**

The STOP mode can be implemented by switching off power supply of 4 MHz oscillator. This can be done with a combination of INRUN (BP42 = "LOW") and SLEEP. During the STOP mode, the I bit in the CCR is set to enable external interrupts. All other registers, memory,

and all I/O lines remain unchanged. This continues until an external interrupt or reset is decoded. After an external interrupt or reset the 4 MHz oscillator starts and generates a reset signal. The program counter is loaded with the reset service routine

Figure 12. Average system power consumption and duty cycle

### 4 Electrical Characteristics

## 4.1 Absolute Maximum Ratings

All voltage are given to  $V_{SS}$ . The circuit is protected against supply voltage reversal for 5 min. typ. @ $I_{max} = 100$  mA.

| Parameters                                     | Symbol             | Value                                  | Unit |

|------------------------------------------------|--------------------|----------------------------------------|------|

| Supply voltage                                 | $V_{\mathrm{DD}}$  | −0.3 to +7.0                           | V    |

| Input voltage (on any pin)                     | V <sub>IN</sub>    | $V_{SS}-0.3 \le V_{IN} \le V_{DD}+0.3$ | V    |

| Output short circuit duration                  | t <sub>short</sub> | indefinite                             | sec  |

| Operating temperature range                    | T <sub>amb</sub>   | -40 to +85                             | °C   |

| Storage temperature range                      | T <sub>stg</sub>   | -40 to +130                            | °C   |

| Thermal resistance (PLCC)                      | R <sub>thJA</sub>  | 110                                    | K/W  |

| Soldering temperature $(t \le 10 \text{ sec})$ | $T_{sd}$           | 260                                    | °C   |

Absolute maximum ratings define parameter limits which, if exceeded, may permanently change or damage the device is required. All inputs and outputs are highly protected against electrostatic discharges. However, precautions to minimize the built-up of electrostatic charges during handling.

For proper operation it is recommended that  $V_{IN}$  and  $V_{OUT}$  be limited to the range:

$$V_{SS}\!\!<\!\!(V_{IN}\,or\,V_{OUT})\!< V_{DD}$$

## 4.2 DC Operating Characteristics

Supply voltage  $V_{DD} = 2.4$  to 6.2 V,  $V_{SS} = 0$  V,  $T_{amb} = +25$ °C unless otherwise specified.

### **4.2.1** Supply Currents

| Parameters                 | Test Conditions / Pins   | Symbol           | Min. | Тур. | Max. | Unit |

|----------------------------|--------------------------|------------------|------|------|------|------|

| Supply current active mode | $V_{DD} = 2.4 \text{ V}$ | $I_{DD}$         |      | 0.5  | 0.7  | mA   |

|                            | $V_{DD} = 6.2 \text{ V}$ |                  |      | 2.7  | 3.2  | mA   |

| Supply current SLEEP       | $V_{DD} = 2.4 \text{ V}$ | I <sub>SLE</sub> |      | 100  | 130  | μΑ   |

| mode                       | $V_{DD} = 6.2 \text{ V}$ |                  |      | 600  | 750  | μΑ   |

| Supply current STOP mode   | $V_{DD} = 2.4 \text{ V}$ | I <sub>STP</sub> |      | 0.08 | 0.1  | μΑ   |

|                            | $V_{DD} = 6.2 \text{ V}$ |                  |      | 0.5  | 0.8  | μA   |

Input voltage pad TE, port 0, 1, 5

| Parameters         | Test Conditions / Pins                   | Symbol   | Min.              | Тур. | Max.              | Unit |

|--------------------|------------------------------------------|----------|-------------------|------|-------------------|------|

| Input voltage LOW  | $V_{DD} = 2.4 \text{ to } 6.2 \text{ V}$ | $V_{IL}$ | $V_{SS}$          |      | 0.2 ×             | V    |

|                    |                                          |          |                   |      | $V_{\mathrm{DD}}$ |      |

| Input voltage HIGH | $V_{DD} = 2.4 \text{ to } 6.2 \text{ V}$ | $V_{IH}$ | 0.8 ×             |      | $V_{\mathrm{DD}}$ | V    |

|                    |                                          |          | $V_{\mathrm{DD}}$ |      |                   |      |

### 4.2.2 Power-on Reset (POR)

| Parameters             | Test Conditions / Pins | Symbol           | Min. | Тур. | Max. | Unit |

|------------------------|------------------------|------------------|------|------|------|------|

| POR voltage            |                        | V <sub>POR</sub> | 1.5  |      | 2.13 | V    |

| POR voltage hysteresis |                        | $\Delta V_{POR}$ |      | 100  |      | mV   |

## **TELEFUNKEN Semiconductors**

## 4.2.3 DC Electrical Characteristics, $V_{DD}$ = 2.4 V @ 25°C

| Parameters                               | Test Conditions / Pins   | Symbol          | Min. | Тур. | Max.  | Unit |  |  |

|------------------------------------------|--------------------------|-----------------|------|------|-------|------|--|--|

| Pad TE                                   |                          |                 |      |      |       |      |  |  |

| Input current<br>n-channel<br>pull-down  | $V_{IH} = V_{DD}$        | I <sub>IH</sub> | 1.1  |      | 5.0   | μΑ   |  |  |

| Bidirectional ports $0.0 - 0.3$          | and 1.0 – 1.2            |                 |      |      |       |      |  |  |

| Input current<br>n-channel<br>pull-down  | $V_{IH} = V_{DD}$        | I <sub>IH</sub> | 1.1  |      | 5.0   | A    |  |  |

| Output current<br>n-channel<br>pull-down | $V_{OL} = V_{SS} + 0.5V$ | $I_{OL}$        | 0.7  |      | 2.6   | mA   |  |  |

| Output currenl<br>p-channel<br>pull-up   | $V_{OH} = V_{DD} - 0.5V$ | I <sub>OH</sub> | -0.6 |      | -2.0  | mA   |  |  |

| Bidirectional port 1.3                   |                          |                 |      |      |       |      |  |  |

| Input current p-channel pull-up          | $V_{IL} = V_{SS}$        | $I_{ m IL}$     | -0.8 |      | -5.3  | μΑ   |  |  |

| Output current<br>n-channel<br>pull-down | $V_{OL} = V_{SS} + 0.5V$ | I <sub>OL</sub> | 0.7  |      | 2.6   | mA   |  |  |

| Output current p-channel pull-up         | $V_{OH} = V_{DD} - 0.5V$ | I <sub>OH</sub> | -0.6 |      | -2.0  | mA   |  |  |

| Input port 5.1 and 5.2                   | Input port 5.1 and 5.2   |                 |      |      |       |      |  |  |

| Input current p-channel pull-up          | $V_{IL} = V_{SS}$        | $I_{ m IL}$     | -6.1 |      | -38.2 | μΑ   |  |  |

## 4.2.4 DC Electrical Characteristics, $V_{DD} = 6.2 \text{ V} \otimes 25^{\circ}\text{C}$

| Parameters                      | Test Conditions / Pins   | Symbol          | Min. | Тур. | Max.  | Unit |  |  |  |

|---------------------------------|--------------------------|-----------------|------|------|-------|------|--|--|--|

| Pad TE                          | Pad TE                   |                 |      |      |       |      |  |  |  |

| Input current                   | $V_{IH} = V_{DD}$        | $I_{IH}$        | 8.2  |      | 36.2  | μΑ   |  |  |  |

| n-channel                       |                          |                 |      |      |       |      |  |  |  |

| pull-down                       |                          |                 |      |      |       |      |  |  |  |

| Bidirectional ports $0.0 - 0.3$ | and 1.0 – 1.2            |                 |      |      |       |      |  |  |  |

| Input current                   | $V_{IH} = V_{DD}$        | $I_{IH}$        | 8.2  |      | 36.2  | A    |  |  |  |

| n-channel                       |                          |                 |      |      |       |      |  |  |  |

| pull-down                       |                          |                 |      |      |       |      |  |  |  |

| Output current                  | $V_{OL} = V_{SS} + 1.3V$ | $I_{OL}$        | 5.0  |      | 13.0  | mA   |  |  |  |

| n-channel                       |                          |                 |      |      |       |      |  |  |  |

| pull-down                       |                          |                 |      |      |       |      |  |  |  |

| Output current                  | $V_{OH} = V_{DD} - 1.3V$ | I <sub>OH</sub> | -5.0 |      | -14.0 | mA   |  |  |  |

| p-channel                       |                          |                 |      |      |       |      |  |  |  |

| pull-up                         |                          |                 |      |      |       |      |  |  |  |

## M43C201

## **TELEFUNKEN Semiconductors**

| Parameters                               | Test Conditions / Pins   | Symbol          | Min. | Тур. | Max.  | Unit |

|------------------------------------------|--------------------------|-----------------|------|------|-------|------|

| Bidirectional port 1.3                   |                          |                 |      |      |       |      |

| Input current p-channel pull-up          | $V_{IL} = V_{SS}$        | $I_{ m IL}$     | -8.0 |      | -51   | μА   |

| Output current<br>n-channel<br>pull-down | $V_{OL} = V_{SS} + 1.3V$ | I <sub>OL</sub> | 5.0  |      | 13.0  | mA   |

| Output current p-channel pull-up         | $V_{OH} = V_{DD} - 1.3V$ | I <sub>OH</sub> | -5.0 |      | -14.0 | mA   |

| Input port 5.1 and 5.2                   |                          |                 |      |      |       |      |

| Input current p-channel pull-up          | $V_{IL} = V_{SS}$        | $I_{ m IL}$     | -58  |      | -366  | μА   |

#### Oscillator 4.2.5

| Parameters                | Test Conditions / Pins                                                              | Symbol           | Min. | Typ. | Max. | Unit |

|---------------------------|-------------------------------------------------------------------------------------|------------------|------|------|------|------|

| Frequency                 | $C_L = 1 pF$                                                                        | f                |      | 4.0  |      | MHz  |

| Integrated input capaci-  |                                                                                     | C <sub>IN</sub>  |      | 10   |      | pF   |

| tance                     |                                                                                     |                  |      |      |      |      |

| Integrated output capaci- |                                                                                     | C <sub>OUT</sub> |      | 10   |      | pF   |

| tance                     |                                                                                     |                  |      |      |      |      |

| Start-up time quartz      | $V_{DD} = 2.4 \text{ V}^{*}$                                                        | $t_{SQ}$         |      | 8    | 90   | ms   |

|                           | $V_{DD} = 2.4 \text{ V}^*)$ $V_{DD} = 3.0 \text{ V}^*)$ $V_{DD} = 5.0 \text{ V}^*)$ |                  |      | 4.5  | 10   | ms   |

|                           | $V_{DD} = 5.0 \text{ V}^{*}$                                                        |                  |      | 2.5  | 4    | ms   |

| Start-up time ceramic     | $V_{DD} = 2.4 \text{ V}^{**}$                                                       | t <sub>SC</sub>  |      | 250  |      | μs   |

|                           | $V_{DD} = 3.0 \text{ V}^{**}$ $V_{DD} = 5.0 \text{ V}^{**}$                         |                  |      | 150  | 300  | μs   |

|                           | $V_{DD} = 5.0 V^{**}$                                                               |                  |      | 150  | 160  | μs   |

\*) Measured with a typical quartz

$C_1 = 3.2 \text{ fF}$   $L_1 = 490 \text{ mH}$   $R_1 = 40$

$C_0 = 1.4 \text{ pF}$

\*\*) Ceramic

$C_1 = 4.4 pF$

$L_1 = 385 \,\mu H$

$R_1 = 8.2$

$C_0 = 36.3 \text{ pF}$

## 4.3 I/O Port Characteristics

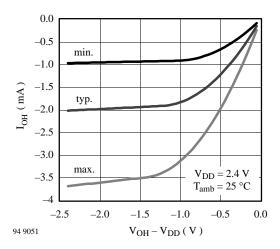

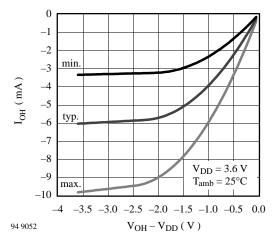

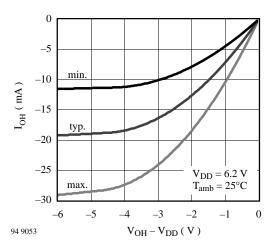

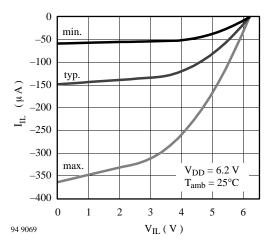

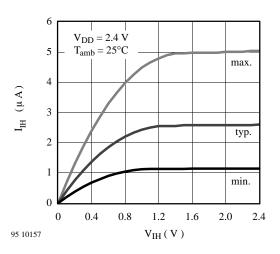

Figure 13. P-channel source current

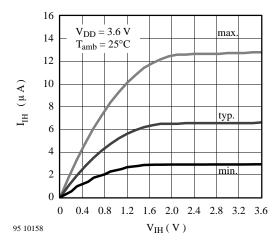

Figure 14. P-channel source current

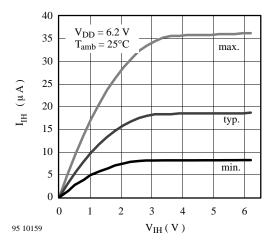

Figure 15. P-channel source current

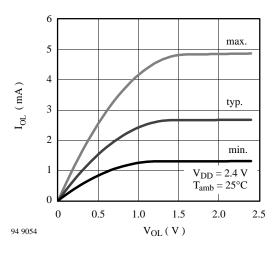

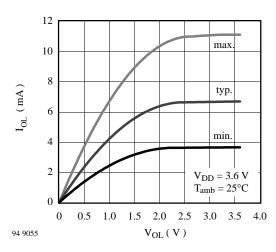

Figure 16. N-channel sink current

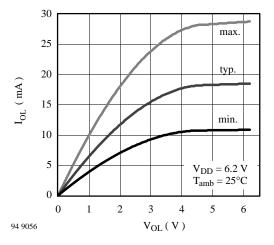

Figure 17. N-channel sink current

Figure 18. N-channel sink current

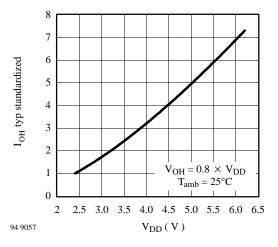

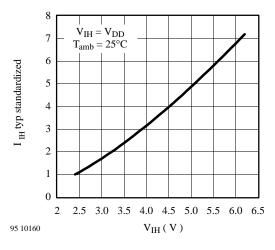

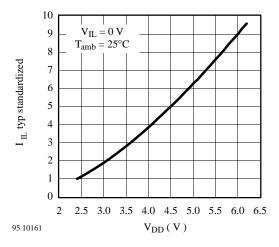

Figure 19. Standardized p-channel source vs. V<sub>DD</sub>

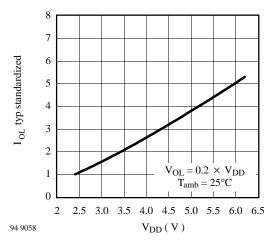

Figure 20. Standardized n-channel sink current vs.  $V_{DD}$

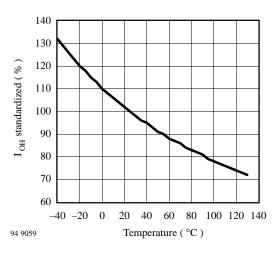

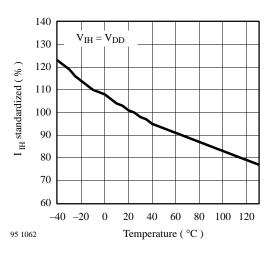

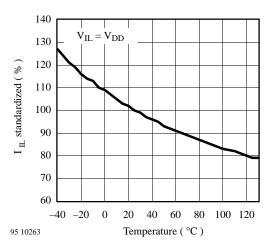

Figure 21. Standardized p-channel source current vs. ambient temperature

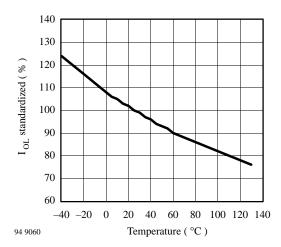

Figure 22. Standardized n-channel sink current vs. ambient temperature

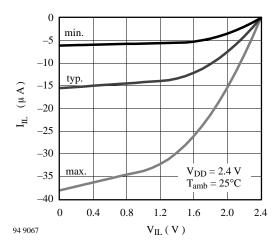

Figure 23. PIN IP5x: p-channel source current

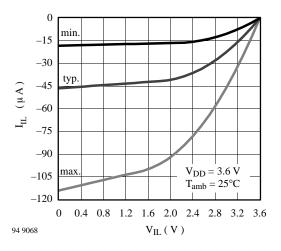

Figure 24. PIN IP5x: p-channel source current

Figure 25. PIN IP5x: p-channel source current

Figure 26. All PINs with pull-down: n-channel sink current

Figure 27. All PINs with pull-down: n-channel sink current

Figure 28. All PINs with pull-down: n-channel sink current

Figure 29. Standardized p-channel source current vs. V<sub>DD</sub>

Figure 30. Standardized n-channel sink current vs.  $V_{DD}$

Figure 31. Standardized p-channel source current vs. ambient temperature

Figure 32. Standardized n-channel sink current vs. ambient temperature

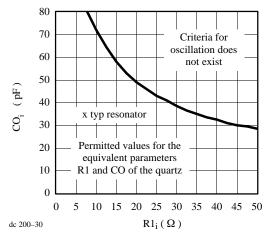

## 5 Characteristics of the On-Chip Quartz / Ceramic Oscillator

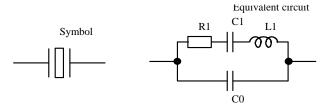

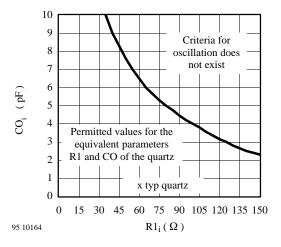

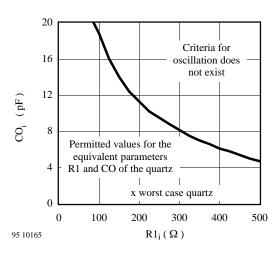

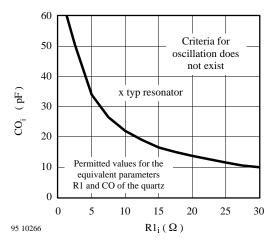

### **Equivalent Circuit of the Quartz and Ceramic Resonator**

The criteria for oscillation depends on R1 and C0 Following diagrams show the equivalent quartz circuits over temperature range -40 to  $+125^{\circ}$ C for two different values of  $V_{DD.}$ . The figure below shows the maximal values of

the equivalent circuit of the ceramic-resonator which are necessary to start up by  $V_{DD} = 3.0 \text{ V}$  and ambient temperature range from -40 to  $+125^{\circ}\text{C}$ . For this test a resonator CSAC4.00 (MURATA) was used.

Figure 33.  $V_{DD} = 2.4 \text{ V}$

Figure 34.  $V_{DD} = 3.0 \text{ V}$

Figure 35.  $V_{DD} = 2.4 \text{ V}$

Figure 36.  $V_{DD} = 3.0 \text{ V}$

**ote:** For pc-board design place the quartz or ceramic resonator nearby the pins. It makes you sure that the parasitic capacities are low ( $\leq 0.5 \text{ pF}$ ).

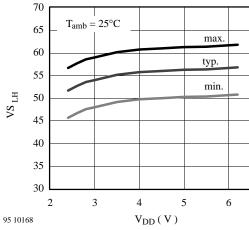

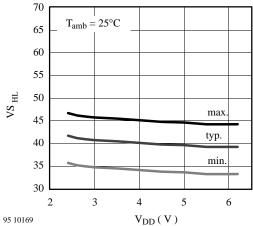

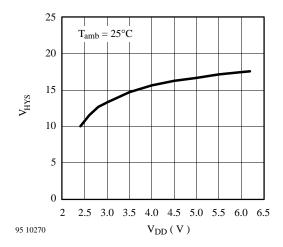

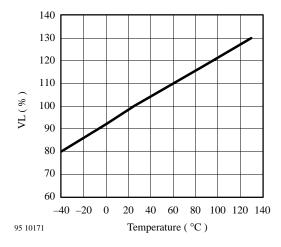

## **Characteristics of the Schmitt-Trigger Inputs**

Figure 37. Voltage switch level for positive edge trigger vs. V<sub>DD</sub>

trigger vs. V<sub>DD</sub>.

Figure 38. Voltage switch level for negative edge

Figure 39. Hystereses in percent of supply voltage vs. V<sub>DD</sub>

Figure 40. Typical switch level vs. ambient temperature

The values of min., typ. and max. for the positive or negative edge trigger are matched.

Note: For recognize a input pulse a minimum pulse time of 50 ns is necessary. The transition time must be  $\leq 10$  ns.

Rev. A1: 26.06.1995 24 (26)

## **TELEFUNKEN Semiconductors**

## **7 Ordering Information**

## **Pin options**

Please select the option setting from the list below.

| Pin       | Output |            | Input   |           |  |

|-----------|--------|------------|---------|-----------|--|

|           | CMOS   | Open Drain | Pull-Up | Pull-Down |  |

| BP00      |        |            |         |           |  |

| BP01      |        |            |         |           |  |

| BP02      |        |            |         |           |  |

| BP03      |        |            |         |           |  |

| BP10      |        |            |         |           |  |

| BP11      |        |            |         |           |  |

| BP12      |        |            |         |           |  |

| BP13      |        |            |         |           |  |

| BP20      |        |            |         |           |  |

| BP21      |        |            |         |           |  |

| BP22      |        |            |         |           |  |

| BP23      |        |            |         |           |  |

| BP30      |        |            |         |           |  |

| BP31      |        |            |         |           |  |

| BP32      |        |            |         |           |  |

| BP33      |        |            |         |           |  |

| IP40-INT6 |        |            |         |           |  |

| IP41-TA   |        |            |         |           |  |

| IP42–TB   |        |            |         |           |  |

| IP43      |        |            |         |           |  |

| NWP       |        |            |         |           |  |

| TE        |        |            |         |           |  |

| ROM code      | e        |            |      |     |

|---------------|----------|------------|------|-----|

| Please insert | ROM CRC. |            |      |     |

|               | Size:    | KByte      | CRC: | hex |

| Approval      |          |            |      |     |

|               | Date:    | Signature: |      |     |

**TELEFUNKEN Semiconductors**

## **Ozone Depleting Substances Policy Statement**

It is the policy of TEMIC TELEFUNKEN microelectronic GmbH to

- 1. Meet all present and future national and international statutory requirements.

- 2. Regularly and continuously improve the performance of our products, processes, distribution and operating systems with respect to their impact on the health and safety of our employees and the public, as well as their impact on the environment.

It is particular concern to control or eliminate releases of those substances into the atmosphere which are known as ozone depleting substances (ODSs).

The Montreal Protocol (1987) and its London Amendments (1990) intend to severely restrict the use of ODSs and forbid their use within the next ten years. Various national and international initiatives are pressing for an earlier ban on these substances.

**TEMIC TELEFUNKEN microelectronic GmbH** semiconductor division has been able to use its policy of continuous improvements to eliminate the use of ODSs listed in the following documents.

- 1. Annex A, B and list of transitional substances of the Montreal Protocol and the London Amendments respectively

- 2. Class I and II ozone depleting substances in the Clean Air Act Amendments of 1990 by the Environmental Protection Agency (EPA) in the USA

- 3. Council Decision 88/540/EEC and 91/690/EEC Annex A, B and C (transitional substances) respectively.

**TEMIC** can certify that our semiconductors are not manufactured with ozone depleting substances and do not contain such substances.

We reserve the right to make changes to improve technical design and may do so without further notice. Parameters can vary in different applications. All operating parameters must be validated for each customer application by the customer. Should the buyer use TEMIC products for any unintended or unauthorized

application, the buyer shall indemnify TEMIC against all claims, costs, damages, and expenses, arising out of, directly or indirectly, any claim of personal damage, injury or death associated with such unintended or unauthorized use.

TEMIC TELEFUNKEN microelectronic GmbH, P.O.B. 3535, D-74025 Heilbronn, Germany Telephone: 49 (0)7131 67 2831, Fax number: 49 (0)7131 67 2423